2. The main characteristic of MAXlOlA ADC chip is the core device of data acquisition, the A / D converter in this system adopts MAXlOlA of MAXIM Company, its highest sampling rate can reach 500 Msps, sampling precision is 8 bit. This article uses two MAXl01A alternate sampling, so that the system reaches the sampling rate of 1 Gsps. The main features of MAXlOlA are as follows:

â—‡ With 500 MHz conversion rate;

â—‡ The effective bit at 250 MHz is 7.0 bit;

â—‡ 1.2 GHz analog input bandwidth;

◇ Error is less than ± 1 / 2LSB INL;

◇ With 50 Ω differential or single-ended input;

◇ With analog input range of ± 250 mV;

â—‡ The data path can be double latched output;

2.2 The principle of MAXl01A (1) Multi-bit conversion MAXl01A uses a parallel structure (that is, a flashing structure) to perform faster multi-bit conversion than ordinary integral ADC. A typical n-bit blinking structure contains (2n-1) comparators whose negative input terminals are evenly arranged from the bottom to the top of the reference network ladder resistor, each occupying an LSB increment value. MAXl01A is a single-chip double-cross parallel quantization chip, which has two independent 8-bit converters. When n = 8, there should be 255 comparators. These converters transfer the results to the two output terminals A and B, and latch them on the alternate negative edge of the input clock.

(2) Tracking / holding The internal tracking / holding amplifier of MAXlOlA improves the performance of obtaining effective data bits and allows analog data to be captured with high accuracy even at high conversion rates. Inside

The Track / Hold circuit provides two important functions for MAXIMA: First, its 4 times rated gain reduces the amplitude of the input differential voltage. For a ± 1.02 V reference source, the input signal is +250

mV; The second is to provide a differential 50 Ω input, making the MAXl01A interface extremely convenient.

(3) Data flow The tracking / holding amplifier inside MAXlOlA provides analog input voltage sampling for the ADC. The T / H amplifier is divided into two parts at the same time, working on alternate clock negative edges. The input clock CLK should meet the requirements of the T / H amplifier, and can also be fed back to the A / D part. The output clock DCLK is used for data timing and is divided by 2 or 10 by the input clock CLK.

2.3 The application of MAXlOlA (1) Although the normal input range is +250 mV, for each input of MAXl01A, the input range to ground is actually ± 500 mV, which extends to include analog The input level of the signal and any DC common-mode voltage. To get a full-scale digital output in differential input mode, a voltage of +250 mv should be added between AIN + and AIN-, that is, AIN + = + 125 mV, AIN-=-125mV (no DC offset). When there is no voltage difference between the analog input terminals, the middle scale digital minute drive will be -250mV, that is, AIN + =-125 mV, and AIN-= + 125 mV, the zero scale digital output code will appear.

(2) Reference The reference resistance of the ADC determines the size and dynamic operating range of the least significant bit (LSB) of the ADC. Usually, the bottom and top of the resistor string are driven by internal buffer amplifiers. Add the RC network to the reference input of the ADC to obtain the best performance. A 33 Ω resistor can be connected to the buffer output stage driving the reference resistor string, and the 0.47 μF capacitor must be connected next to the buffer output stage resistor. This combination of resistor and capacitor must be within 0.5 inches (1.27 cm) of the MAX101A package. The noise of any termination point will directly affect the code detection and reduce the effective data bit index of the ADC. 3) Clock CLK and DCLK

All input clocks and output clocks of MAXl01A are differential. The input clocks CLK and DCLK are the basic timing signals of MAX101A. CLK and DCLK are locked to the internal circuit through an internal 50 Ω resistance transmission line. Only a pair of CLK and DCLK input terminals are driven, while the other pair of coupling terminals is connected to -2 V through the 50 Ω transmission line. For simple circuit connections, any pair of input terminals can be used as driven terminals. DCLK and / DCLK are the output clocks generated by the input clock and are used for the internal output timing of data packets A and B (Group A data is valid after the rising edge of DCLK. Group B data is valid after the falling edge). In normal mode, they are clock signals at half the input clock speed. MAXl01A can work on the input clock frequency up to 500 MHz.

(4) Output mode control (DIVl0)

When the DIVl0 pin of MAXl01A is grounded, it works in detection mode. At this time, the input clock is divided by 10, which reduces the output data and clock frequency to 1/5, but still ensures that the duty cycle of the output clock is 50%, and the clock connected to the output phasing remains unchanged, so every 5 Four of the input samples are discarded. Conversely, when the DIVlO pin is left floating, it is pulled low by the internal resistance, and MAX-lolA works in normal mode.

(5) Wiring, grounding and power supply During normal operation, MAxl01A requires a positive power supply of + 5 × (1 ± 0.01) V and a negative power supply of −5.2 × (1 ± 0.01) V. By using high-quality 0.1μF and 0.01μF ceramic capacitors, the VTT and Vcc power supply is bypassed and grounded as close as possible to the pin. All ground pins need to be connected to the ground plane to optimize noise immunity and improve device application accuracy.

3 Data cache module design The data cache uses the FLEXlOKE series CPLD of Ahera Company. This design uses FLEXlOKE devices to implement high-speed FIFO. Since the input and output clock frequency of FIF0 as a data buffer cannot be the same, a dual-clock FIFO must be used. And this type of device is powered by low voltage, which greatly reduces the power consumption of the system and improves the flexibility and reliability of the system.

The system introduced in this article uses VHDL hardware description language to program FLEXlOKE, and the programming environment is MAX + PLUSâ…¡V9.6.

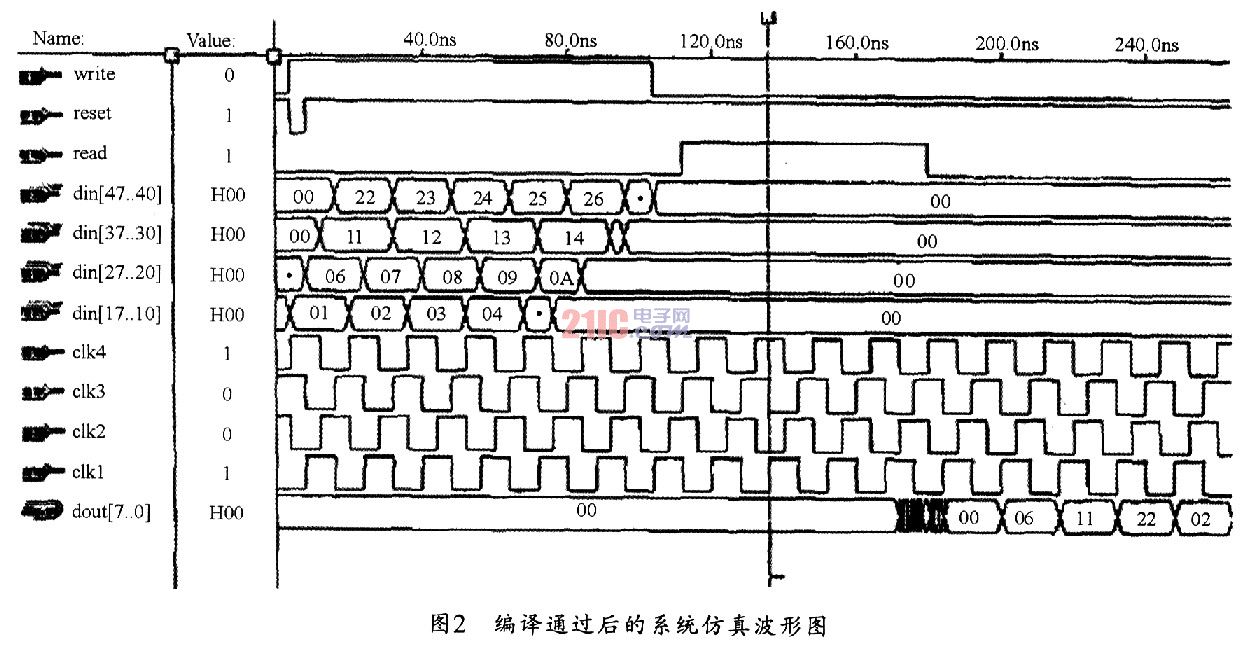

VHDL programming adopts modular design. First build 4 modules, namely FIF0, MUX, counterl, counter2. Among them, FIFO can call lpm-FIF0 (dualClock) to modify some of the key parameters to meet the requirements, or you can manually write a program to achieve, here the method of calling the macro module. It is worth noting that the input and output clock frequencies of the FIFO are different, so the dual clock FIF0 must be used. MUX, counterl, counter2 are multiplexers and frequency dividers (counters) used in conjunction with FIF0, and their source programs should be written manually. After several sub-modules are completed, a general system module (system) should be created to call the sub-modules to complete the definition of the system ports and the description of the logical relationship between the various sub-modules in the system module. This design is conducive to the integration of logic design, thereby providing convenience for subsequent improvements. Figure 2 is the system simulation waveform diagram after the compilation is passed.

4 Conclusion This article takes DRFM design as the core, and focuses on the design ideas and methods of the DRFM data acquisition front end. In the field of ultra-high-speed data acquisition, sampling speeds of hundreds of megabytes or even 1 GHz are not only difficult at home, but also abroad. Using CPLD based on SRAM can effectively avoid the impact of high power consumption and high overhead brought by using high-speed FIFO as a buffer. The data cache can be implemented in one chip, which reduces the complexity of the hardware and reduces the power consumption of the system. More worthy of attention is that this type of CPLD has icr, that is, the circuit can be reconfigured, and the circuit function can be modified by programming it, which lays a good foundation for subsequent system improvement.

Vacuum Cleaner Ac Dry-Wet Motor

Vacuum Cleaner Ac Dry-Wet Motor,Vacuum Electric Cleaner Ac Motor,Wet Dry Vacuum Cleaner Motor,Wet And Dry Vacuum Cleaner Motor

Zhoushan Chenguang Electric Appliance Co., Ltd. , https://www.vacuum-cleaner-motors.com