0 Preface

Electrocardiogram (ECG) can objectively reflect the physiological conditions of various parts of the heart, and is also the main basis for diagnosing heart diseases. Because of its easy detection and better intuitiveness, it has been widely used in clinical medicine. Research and application [1, 2]. Since the first electrocardiograph was used in clinics in 1906, various forms of electrocardiographs have appeared one after another. Traditional electrocardiogram detection instruments are mostly designed with single chip microcomputer and PC as the core design. The system is cumbersome and the detection method is single, which is not conducive to the improvement of system integration and miniaturization, or causes inconvenience of the system [3]. Due to the rise of wearable devices and mobile medical care, ECG monitors are developing towards miniaturization, portability, and intelligence [4].

This paper designs an ECG signal detection and processing system based on a System-on-Chip Field Programmable Gate Array (SoC FPGA), and realizes the ECG signal detection system through A/D hybrid design and software-hardware co-design. The signal acquisition is completed by the analog front-end circuit, using the advantages of SoC FPGA reconfigurability and software-hardware co-design, A/D conversion, VGA display, data storage and algorithm processing are performed on the signal through software programming, thereby realizing signal acquisition, display, and storage An ECG detection and processing system that integrates multiple functions such as processing and processing.

1 ECG signal detection system design

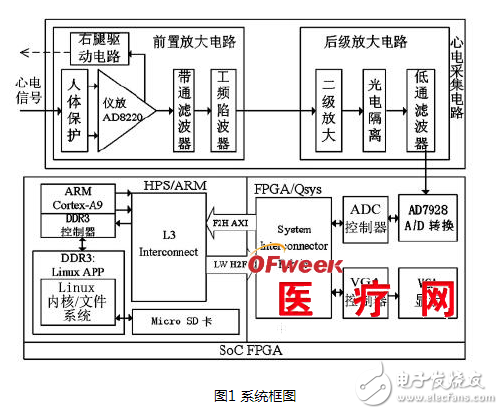

The ECG signal detection and monitoring system is a hybrid system of analog and digital, which is mainly divided into the body surface ECG signal acquisition circuit and the ECG signal digital processing system with SoC FPGA as the core. The acquisition circuit is connected to the medical lead wire to pick up the ECG signal through the patch electrode. The ECG signal is amplified by the acquisition circuit and processed by analog filtering and then enters the SoC FPGA. It is first controlled by the Linux-based application on the ARM embedded hard core on the HPS side. A/D conversion is converted into a digital signal for VGA display on the FPGA side, and the digital signal is transmitted to the HPS side at the same time, and the digital signal can be algorithmically processed and stored on the MicroSD card. SoC FPGA software-hardware collaborative development method is extremely convenient for hardware design and software development of ECG signal follow-up algorithm processing. The overall architecture of the system divided by functional modules is shown in Figure 1.

1.1 Body surface ECG signal acquisition circuit

The amplitude range of normal ECG signal is 10 μV~5 mV, the typical value is 1 mV, and the frequency range is 0. 05~100 Hz, and the ECG signal is very sensitive to noise. Therefore, the ECG signal acquisition circuit needs to have high input impedance, high common mode rejection ratio, low noise and low drift performance. The body surface ECG acquisition circuit is composed of a pre-amplification circuit and a post-amplification circuit.

1. 1.1 Pre-amplification circuit

The pre-amplification circuit mainly amplifies and de-noises the picked-up ECG signal in order to facilitate the subsequent amplification and processing. The noise in the ECG signal mainly includes power frequency interference, myoelectric interference, baseline drift and high frequency noise.

1) Pre-amplification circuit design

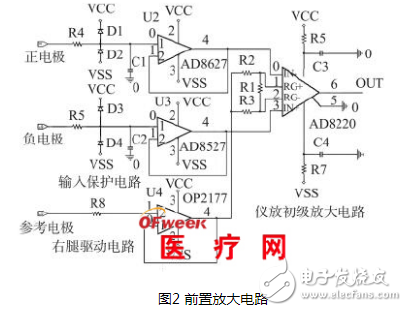

The preamplifier circuit is composed of a preamplifier circuit, a bandpass filter circuit and a 50 Hz power frequency trap circuit. The preamplifier circuit also includes an input protection circuit, a right leg drive circuit and an instrument operational amplifier circuit, as shown in the figure 2 shown.

Since the system needs to be connected to the body surface to collect signals, it is necessary to consider the problem of human body protection during the signal collection process. In the system, a transient voltage suppressor (TVS) diode with a high withstand voltage is selected to be added to the input stage of the acquisition circuit. To protect the human body and circuits. The right leg drive circuit is used to connect the reference electrode in collecting the ECG signal, which can effectively eliminate the common mode interference in the collected signal [5]. The operational amplifier circuit of the instrument completes the primary amplification of the ECG signal, and at the same time has the characteristics of high input impedance, high common mode rejection ratio, low noise and low drift. Comprehensive consideration, choose ADI's precision instrument operational amplifier AD8220 chip, in order to prevent saturation distortion, the pre-stage gain is set to 20 times [6].

2) Elimination of power frequency interference and baseline drift

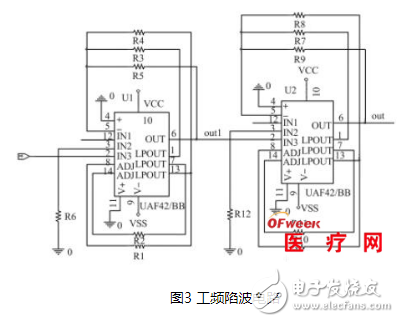

The ECG signal picked up by the acquisition circuit has low-frequency baseline drift and high-frequency interference, as well as 50 Hz power frequency interference within the frequency range of the ECG signal. These noises have a great influence on the extraction of the ECG signal. The bandpass filter and 50 Hz power frequency notch filter based on the universal active filter module UAF42 are designed. The passband of the band-pass filter circuit is 0. 05~100 Hz, filter out low frequency interference and high frequency noise such as baseline drift, power frequency notch filter can effectively filter power frequency noise. Filters of various types and frequency characteristics can be conveniently designed through UAF42. You only need to calculate an external resistor with a suitable resistance value. The design requirements can be well met through simple connections, eliminating the need for active filters. The selection and matching of capacitors and resistors in the design [7]. The circuit diagram of the power frequency notch filter is shown in Figure 3.

Two UAF42 chips are used to form a fourth-order notch filter to increase the notch depth. The power frequency notch circuit is designed with a Q value of 50 and a 50 Hz notch depth of -110 dB. Compared with the traditional double T notch filter, the center frequency of this notch filter can be set during the design, eliminating the need to debug the center frequency of the notch. In addition, you only need to connect the resistor whose resistance value is calculated during the design, eliminating the need for capacitor selection and matching.

1. 1.2 Post-amplification circuit

The post-amplification circuit is composed of a two-stage amplifying circuit, a photoelectric isolation circuit and a low-pass filter circuit. In the preamplifier circuit, neither the gain value of the instrument operational amplifier nor the gain value of the bandpass filter can be set too high to avoid excessive amplification of the amplitude and oscillations after the noise enters, which will seriously interfere with the effective signal, so, The overall gain range is 1 000 to 3 500, and the gain of the amplification system will be realized by a multi-stage gain circuit. The two-stage amplifying circuit can bring the gain of the system to the set value, and the operational amplifier is connected to the form of voltage negative feedback to control the gain of the overall circuit. The photoelectric isolation circuit uses a low-cost precision capacitive linear optocoupler chip ISO124 to achieve electrical isolation between the front and rear circuits and avoid the influence of feedback noise. The low-pass filter is mainly to eliminate the high-frequency noise introduced by the photoelectric coupling, and to prevent the high-frequency noise of the previous circuit from entering the digital circuit board. The post-amplification circuit realizes the electrical isolation between the analog circuit board and the digital circuit board.

1. 2 ECG signal SoCFPGA digital processing system design

1. 2. The structure and characteristic of 1 SoCFPGA

This paper uses the 28 nm process-based Cyclone V SoC FPGA introduced by Altera as the hardware design platform. This new SoCFPGA combines two separate and different types of chips to combine the ARM-based hard core processor system (hard core processor system). processor system, HPS) is integrated in the FPGA architecture [8].

Use Altera's embedded system design suite (embedded designsuite, EDS) SoC for software and hardware design and development. Use Qsys, a new generation SOPC tool integrated in QuartusII, to design hardware modules. It can automatically generate interconnection logic and connect intellectual property (IP) functions and subsystems. SoC EDS also provides the conversion from Qsys hardware system information to software development. The tool makes the software and hardware design link up and supports Linux application development. With the help of DS-5, the software design from boot code and kernel transplantation to Linux application program can be completed [9].

1.2.2 ECG signal digital processing system

The digital system includes A/D conversion module, VGA display module, data storage module and algorithm processing module. HPS and other hardware modules in SoC FPGA can be configured through Qsys and Quartus II for hardware design. Qsys and Quartus II compilation can generate information files required for software design. Transplant the embedded Linux system, download the sof file, and use DS-5 to develop the system software engineering based on Linux [10].

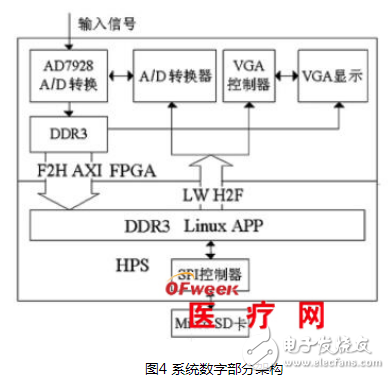

The A/D converter of the system uses the 8-channel 12-bit high-precision low-power A/D converter chip AD7928 of ADI, and the conversion rate is 1MSPS. The sampling rate recommended by the American Heart Association is 500 Hz, but in practice, different applications have different sampling rates, generally 125 to 1 000 Hz, 200 Hz or 250 Hz is often used for monitoring, and 400 to 500 Hz for auxiliary analysis. The ECG HOLTER is generally 125~200 Hz, and this system uses 200 Hz. Write a program to control A/D conversion and data buffering, generate line synchronization signals and column synchronization signals needed to control VGA, blanking signals, clock signals, and RGB signals to make the screen work normally. The embedded Linux file system supports the writing and reading of Micro SD card data, and the digital signal is transmitted to the HPS terminal through the AXI bridge. The software engineering realizes the algorithm processing of the ECG signal and the data storage of the Micro SD card. The structure diagram of the digital part of the system is shown in Figure 4.

2 System test

After the system design is completed, debug and test the front-end acquisition circuit and the overall system. The medical patch-type Ag/AgCl ECG electrode is placed in a three-lead mode and connected to the ECG signal acquisition system through a medical lead wire for testing.

2.1 Analog front-end acquisition circuit test

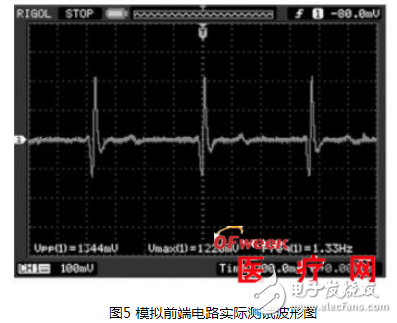

The subject wears ECG electrodes, connects to the analog front-end acquisition circuit with medical lead wires, and connects to the oscilloscope at the back end. After the signal is stable, the ECG signal waveform can be observed on the oscilloscope. Figure 5 is the analog front-end circuit Actual test waveform.

2. 2 Overall system test

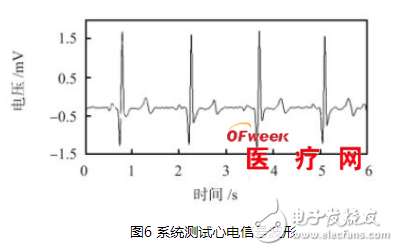

Connect to the overall system, run the software project, the system stores the ECG signal for a period of time, take out the Micro SD card, read the stored data and restore the ECG signal waveform as shown in Figure 6.

3 ECG signal algorithm processing

ECG signal algorithm processing becomes more and more extensive with the application of intelligent medical treatment. In specific application environments such as health monitoring and disease diagnosis, traditional algorithm processing is implemented based on hardware. Hardware-based implementation methods are generally more difficult and resource-intensive. The transplantation of embedded Linux systems greatly facilitates the processing of ECG signal algorithms. Software implementation. The wavelet denoising and QRS wave detection of ECG signals are realized in software engineering.

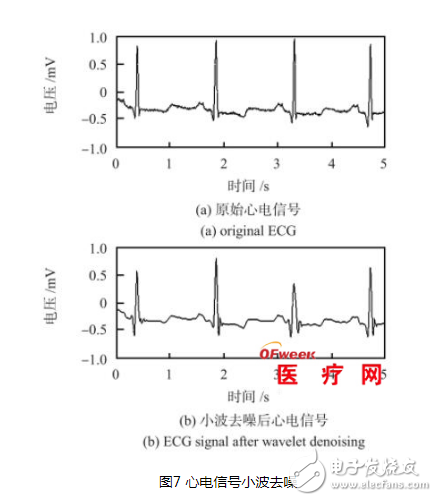

3.1 ECG signal denoising based on wavelet analysis

The method of wavelet analysis is used to denoise the ECG signal. Wavelet analysis can analyze the signal in the time domain and the frequency domain at the same time, and has the function of multi-resolution analysis, so it can effectively distinguish the abrupt part and noise of the signal on different decomposition layers. After the original ECG signal with noise is decomposed by wavelet, the noise is mainly concentrated in the high-frequency wavelet coefficients. The wavelet coefficients containing useful signals have a larger amplitude but a small number; while the wavelet coefficients corresponding to noise have a small amplitude and number More. Based on the above characteristics, the unbiased likelihood estimation threshold is selected to process the wavelet coefficients, and then the signal is reconstructed to achieve the purpose of noise elimination. Figure 7 shows the comparison of ECG signal before and after wavelet denoising, the signal-to-noise ratio can reach 121 dB.

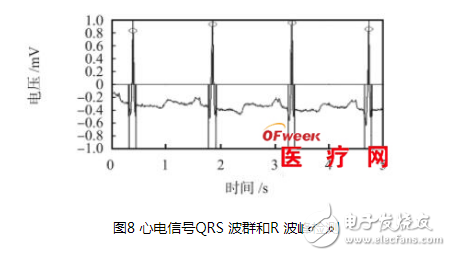

3.2 QRS wave detection based on wavelet analysis

According to the theory of wavelet transform, the singular point of a signal corresponds to a pair of positive modulus maximum and a negative modulus maximum of its wavelet transform, and its position corresponds to the zero-crossing point of the positive and negative modulus maximum. The specific algorithm is to find The maximum modulus of wavelet transform is judged as QRS complex when the calculated signal modulus is greater than a certain threshold. At the same time, this threshold is also adaptively updated with the calculation result. After the QRS complex is determined, the zero-crossing point can be detected to determine the specific R-wave position. Figure 8 shows the ECG signal QRS complex detection and R wave peak location.

After the wavelet analysis of the ECG signal detects the R wave peak and other characteristic points, the extracted characteristic values ​​can be used for pattern recognition and classification, for example: Use BP neural network to classify the shape of the ST segment waveform of the ECG [11].

4 Conclusion

The ECG signal detection system based on SoC FPGA designed in this paper can collect ECG signals well, and realize the extraction, display, storage and processing of ECG signals. The test shows that: The analog front-end circuit of the system can collect the ECG signal that is clearly amplified to a suitable multiple. The overall test of the system proves the feasibility of the design. The development method of SoC FPGA software and hardware combination can realize the algorithm processing of the ECG signal, make the design more flexible, provide convenience for the processing and analysis of the ECG signal, and also provide the possibility for the realization of intelligent medical treatment.

LED Wall Wash Light

Wall Wash Light Series Include 36x12w LED Wash light, 19x15w Led wash light; Both is hot selling in the lighting market.

36X12W RGBW 4 IN 1/5 IN 1/6 IN 1 /LED Wash Moving Head Light

Specification:

Pure bright in color effect, excellent color mixing, good heat cooling

36 pcs 12W RGBWA+UV 6in1 LED, 36 pcs 10W RGBWA 5in1 LED, 36 pcs 10W RGBW 4in1 LED

10-60 zoom angle, narrow beam effect to wide wash effect, functional in usage.

Small size, easy to carry and install, each unit weighs only 9kg

Linear smooth dimmer from 0-100%, 1-20 times strobe per second, flicker-free for TV and films.

Suitable for mobile productions, events, parties, stage installations, theater, musical concert, TV studios.

Our company have 13 years experience of LED Display and Stage Lights , our company mainly produce Indoor Rental LED Display, Outdoor Rental LED Display, Transparent LED Display,Indoor Fixed Indoor LED Display, Outdoor Fixed LED Display, Poster LED Display , Dance LED Display ... In additional, we also produce stage lights, such as beam lights Series, moving head lights Series, LED Par Light Series and son on...

Wall Wash Light Series,Disco Light,Led Washer Light,Moving Head

Guangzhou Chengwen Photoelectric Technology co.,ltd , https://www.cwledpanel.com