Ethernet is the most basic and popular LAN networking technology. In order to adapt to various new services such as streaming video, the rate is also increasing. Gigabit Ethernet is a technology based on the Ethernet standard. It has the characteristics of high efficiency, high speed and high performance. At present, the construction of enterprise LAN and even metropolitan area network will adopt Gigabit Ethernet technology as the preferred high-speed network technology. Gigabit Ethernet protocol analysis technology has been developed with the rapid development of computer technology, modern communication technology and network technology. It can cope with unexpected events in information networks, quickly determine network defects and attack sites, and respond to emergencies. The role of support. At the same time, with the wide application and deepening of TCP/IP (Transmission Control Protocol/Internet Protocol), the construction, maintenance and fault diagnosis of TCP/IP computer network faces enormous challenges, and the application of Gigabit Ethernet protocol analysis technology is urgently needed. .

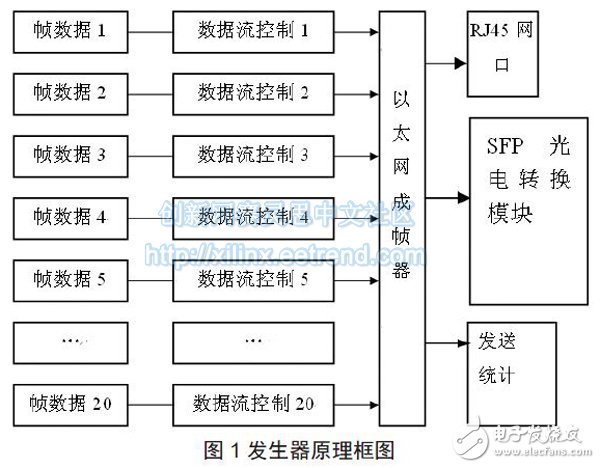

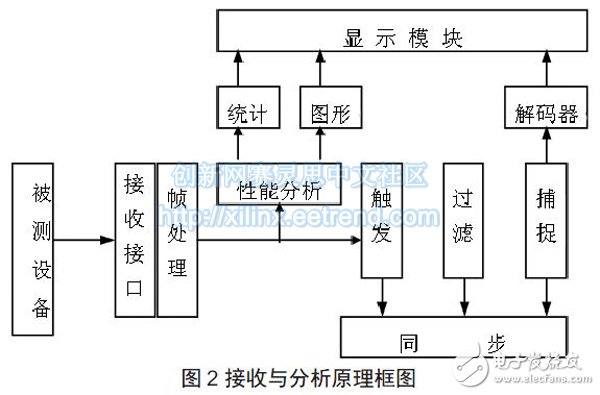

1 Working principleThe Gigabit Ethernet protocol analysis technology introduced in this paper is based on FPGA (Field-Programmable Gate Array) design technology, supporting 10M/100M/1 000M electrical port and optical port test, using RJ45 and SFP optical port connectors; responsible for the physical layer and Data frame editing, generation, capture, filtering, triggering, decoding, and analysis processing of the data link layer. Protocol frames above the IP layer have software operating according to the IEEE802.3 protocol standard. Figure 1 and Figure 2 show the block diagram of the transmitting part, receiving and analyzing part of the scheme respectively.

Gigabit Ethernet Protocol Test The internal design part of the FPGA can be divided into a transmit part, a receive analysis part, and an interface chip register management part. Among them, the sending part completes the functions of sending, editing and generating various Ethernet data streams. According to the test requirements, the sending part can generate abnormal data such as arbitrary MAC address, IP address, error check and error insertion. Among them, there are many types of MAC address and IP address settings, which can be set to static, incremental, decrement, random, etc.; the receiving analysis part performs Ethernet data stream statistics, capture, decoding analysis, signal performance statistics, etc.; according to test needs, receive Some can choose to capture and count the required MAC address, IP address, wrong check type and error insertion type, etc. The filter conditions and trigger conditions that can be set are MAC address, IP address, graph 1, graph 2 Protocol type and error type, etc. The interface chip register management section completes the read/write operation and management of the interface chip BCM5421 register and the serial/parallel and parallel/serial conversion functions.

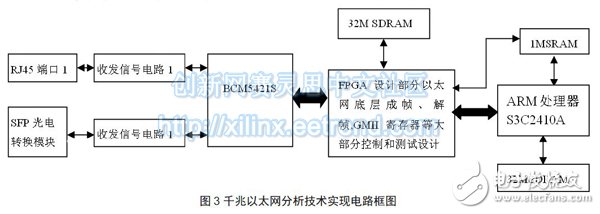

2 design implementationThe Gigabit Ethernet protocol analysis technology described in this article is implemented by a hardware platform combining a Gigabit Ethernet transceiver BCM5421 and a large-scale FPGA. Because Gigabit Ethernet supports both electrical and optical interface modes, complex Ethernet protocols, high Gigabit speed, and large logic control, it is very difficult in FPGA design and PCB layout design. The block diagram of the specific design implementation is shown in Figure 3.

The Gigabit Ethernet signal is sent to the interface chip through the transceiver processing circuit, and the interface chip performs signal validity, collision, encoding/decoding, lighting, etc. on the signal, and then is sent to the FPGA in an 8-bit serial data stream. In the FPGA, it is necessary to complete the editing, generation, data editing, error insertion, parallel/serial conversion, and transmission mode setting of various Ethernet frames in the MAC layer transmission part, and complete monitoring and capturing of various Ethernet frames in the MAC layer receiving part. , filtering, decoding, finding errors and evaluating performance, etc., MAC layer interface chip register management, read and write control, etc.; CPU and hardware for SRAM, SDRAM read and write, storage operations, etc., the specific implementation process is as follows.

2.1 Gigabit Ethernet Protocol Analysis Interface Circuit Design The Ethernet test module uses two interface modes: the RJ45 electrical port and the optical port of the SFP photoelectric conversion module. The technical implementation adopts the BCM5421S of the interface transceiver chip BROADCOM, which fully supports IEEE802.3, auto-negotiation, collision detection test, encoding/decoding, serial/parallel conversion, etc., and conforms to 10BASE-T, 100BASE-TX and 1000BASET. standard. At the same time, support RGMII, GMII, MII, TBI, RTBI, SGMII and SerDesMAC interface.

1500W Cloth Dryer And Fan Heater

1500W Cloth Dryer And Fan Heater,Ptc Fan Heater,Ptc Tower Heater,Ptc Electric Fan Heater

Foshan Shunde Josintech Electrical Appliance Technology Co.,Ltd , https://www.josintech.com