design background:

Frequency division has always played a very important role in the design of fpga. When it comes to frequency division, I believe that many people have already thought of using a calculator to calculate the desired clock frequency, but the problem is that only the counter is used to divide the frequency. Frequency, can only achieve even frequency division, and if I need to divide the frequency of the three, five, seven, and so on odd-numbered frequency division, then what to do? Here, let me introduce an arbitrary integer frequency division can be achieved The method, this method is also the same use of the counter to calculate, when it is different from the even frequency division is an arbitrary integer frequency division using two counters to achieve.

Â

Design principle : Â

This design is mainly to design an adjustable frequency divider, I can set its parameters, you can adjust the output of the duty cycle, the meaning of the duty cycle is the number of high cycle. We are instructed to calculate high time and low time, which is actually controlled by two counters.

Â

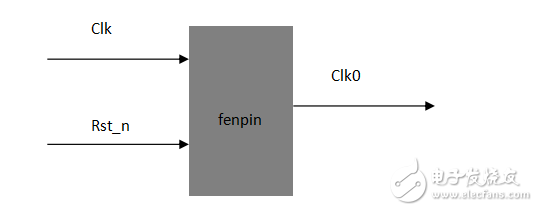

Design architecture diagram :

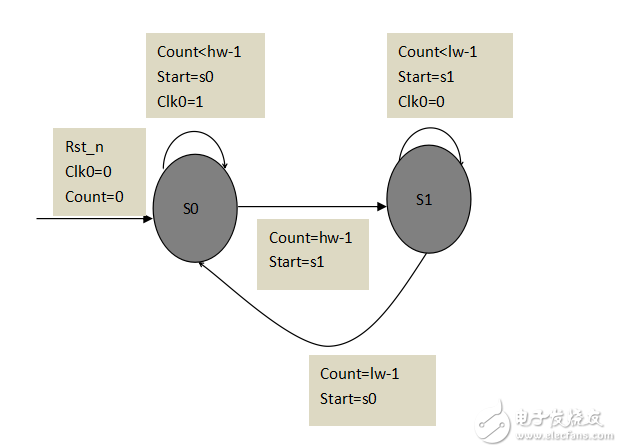

State transition diagram

By counting the two counters, one calculates the next state of the jump, and waits until the next counter counts up and returns to the first state, thereby completing the design of an arbitrary frequency divider.

Â

Design code :

Design module

Â

0 Â Module fenpinqi ( clk , rst_n , clk0 );

1 Â Input clk ;

2 Â Input rst_n ;

3 Â

4  Output  Reg clk0 ;

5 Â

6 Â Parameter HW = Â 7 Â ; Â Â Â Â Â // One high 7

7 Â Parameter LW = Â 3 Â ; //The low level is 3 or 5M clock

8 Â

9 Â Localparam s0 = Â 1'b0 ; Â Â Â Â // Define two states

10 localparam s1 = Â 1'b1 ;

11

12 reg state ;

13 reg  [ 2 : 0 ] count ;

14

15 always  @( posedge clk or  negedge rst_n)

16 if (! rst_n )

17 begin

18 state <= Â 1'b0 ;

19 count <= Â 3'b0 ;

20 clk0 <= Â 1'b0 ;

21 end

22 else

23 begin

24 case  ( state )

25 s0 : begin

26

27 if ( HW + Â 1 Â > Â 1 ) / / To determine whether the HW is 0

28 if ( count < HW - 1 Â ) Â Â // Counter counts high

29 begin

30 clk0 <= Â 1'b1 ; Â Â // generates a high level

31 count <= count + Â 1'b1 ;

32 end

33 else

34 begin

35 count <= Â 1'b0 ;

36 state <= Â 1 ;

37 end

38 end

39 s1 : begin

40 if ( LW + Â 1 Â > Â 1 ) Â Â / / Determine if LWW is 0

41 if ( count < LW - 1 ) // Counter counts low

42 begin

43 clk0 <= Â 1'b0 ; Â Â Â Â // generates a low level

44 count <= count + Â 1'b1 ;

45 end

46 else

47 begin

48 count <= Â 1'b0 ;

49 state <= Â 0 ;

50 end

51 end

52 default : state <= Â 0 ;

53 endcase

54 end

55 Â Endmodule Â

Â

Test module

0  `timescale  1ns / 1ps

1 Â Module fenpinqi_tb ();

2 Â

3 Â Reg clk ;

4 Â Reg rst_n ;

5 Â

6 Â wire clk0; Â Â Â Â Â Â Â // Define the output as wire type

7 Â

8 Â Parameter HW = Â 5 ;

9 Â Parameter LW = Â 1 ;

10

11 initial  Begin

12 clk = Â 1'b1 ;

13 rst_n = Â 1'b0 ;

14

15 # 200.1 rst_n = Â 1'b1 ;

16 # 2000 Â $stop ;

17 end

18 always  # 10 clk =  ~ clk ;     // Generate 50M clock

19

20 fenpinqi #(. HW ( HW ),. LW ( LW )) Â Â Â // instantiation, we can change the duty cycle here, and frequency

21 fenpinqi_dut (

22 . clk ( clk ),

23. Rst_n (rst_n),

24. Clk0 (clk0)

25 );

26 endmodule Â

Â

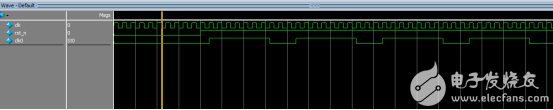

Simulation diagram :

In the figure, we can see that the output of output clk0 is 7 high and 3 low by the number of rising edges , which is in line with our design.

As we all know that the parents all over the world pay more attention on children education, so more and more businessman do education laptop deals, therefore education laptop is becoming one of the most important fields no matter on customizing laptop or brand one. There are different series according to students ages, 14 inch celeron windows 10 education laptop for elementary students, 15.6 inch j4125 intel education laptop for middle or high school students or normal business jobs, 15.6inch 10th or 11th windows laptops for students in college or professional business or online teaching, etc. Besides, 15.6 inch 10th with 2gb graphics Programming Laptop or 16.1 inch i5 i7 i9 9th HQ GTX 1650 windows laptop for programming also available.

So you just need to share the education laptop price and parameters matched prefer, then right valuable information provide directly for you.

You are always welcome whatever only consult or have purchase plan recently.

Education Laptop,Education Laptop Deals,Windows 10 Education Laptop,Education Laptop Price,Intel Education Laptop

Henan Shuyi Electronics Co., Ltd. , https://www.shuyioemminipc.com